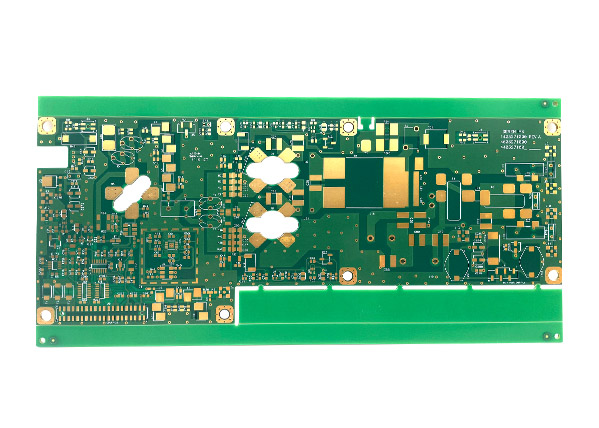

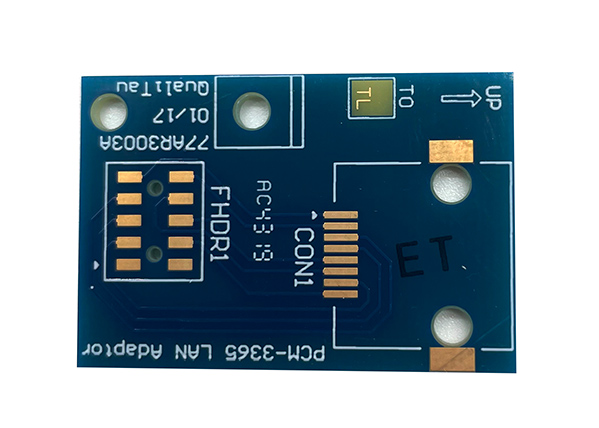

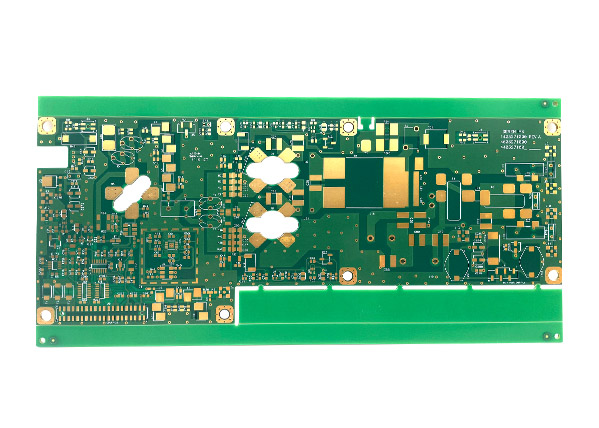

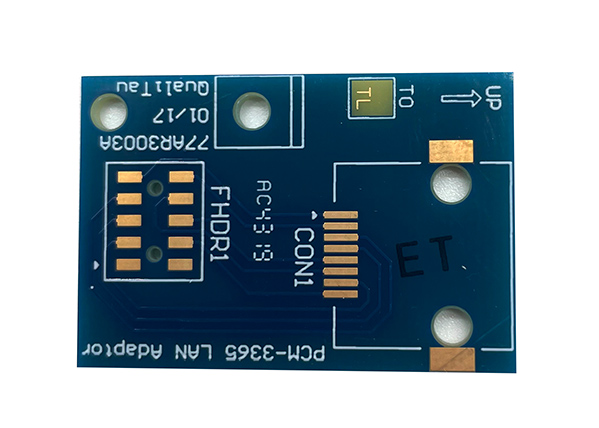

10 Charakteristike vun héich Zouverlässegkeet PCB,

1. 20μm Lach Mauer Koffer deck vun Gedréckt Circuit Verwaltungsrot ,

Virdeeler: Verbessert Zouverlässegkeet, dorënner verbessert Z-Achs Expansioun Resistenz. Risiken fir dat net ze maachen: Schlag Lächer oder Ausgasung, elektresch Konnektivitéitsprobleemer wärend der Montage (Trennung vun banneschten Schichten, Broch vu Lachmaueren), oder méiglech Ausfall ënner Laaschtbedéngungen am aktuellen Gebrauch.

2. Nee Schweess Reparatur oder Open Circuit Reparatur Virdeel: Perfekt Circuit garantéiert Zouverlässegkeet a Sécherheet, keen Ënnerhalt, kee Risiko. Risiko fir dëst net ze maachen: Wann falsch gefléckt, wäert Dir en oppene Circuit op de Bord erstellen.Och wann se "richteg" reparéiert ginn, besteet e Risiko fir Ausfall ënner Laaschtbedéngungen (Vibratioun, asw.), déi am aktuellen Gebrauch versoen. 3. Benotzt international bekannte CCL, Virdeeler: Verbessert Zouverlässegkeet, Liewensdauer a bekannt Leeschtung. Risiken fir dëst net ze maachen: Mat enger schlechter Qualitéitsplacke wäert d'Liewensdauer vum Produkt staark verkierzen, a gläichzäiteg schlechte mechanesch Eegeschafte vum Blat bedeit datt de Board net wéi erwaart ënner de montéierte Konditiounen, zum Beispill: héich Expansioun Eegeschafte kënnen zu Delaminatioun féieren, oppe Circuit a warping buckling Problemer, a geschwächt elektresch Eegeschafte kënnen zu enger schlechter Impedanzleistung féieren. D'Materialien vun ABIS PCB Fabréck sinn all aus gutt-bekannt Gewalt an auslännesch Verwaltungsrot Fournisseuren, an hunn laangfristeg strategesch Zesummenaarbecht Relatioune mat Fournisseuren erreecht Fourniture ze stabiliséieren. 4. Benotzt héichwäerteg Tënt Virdeeler: Assuréieren d'Qualitéit vum Circuit Board Dréckerei, verbessert d'Fidelitéit vun der Bildreproduktioun a schützt de Circuit. Risiko fir dat net ze maachen: Schlecht Qualitéit Tënt kënne Adhäsioun, Fluxresistenz a Hardnessproblemer verursaachen.All dës Probleemer kënnen d'Lötmaske verursaachen aus dem Bord ze trennen a schliisslech zu Korrosioun vum Kupferkreeslaf féieren.Schlecht Isolatiounseigenschaften kënne Kuerzschluss verursaachen wéinst zoufälleg elektresch Kontinuitéit / Bogen.

5. Iwwerschreiden d'Propperheet Ufuerderunge vun IPC Spezifikatioune Virdeel: Verbessert PCB Propretéit verbessert Zouverlässegkeet. Risiken fir dëst net ze maachen: Reschter um Bord, Opbau vum Solder kënnen e Risiko fir d'Lötmaske presentéieren, ionesche Reschter kënnen d'Korrosioun vun der Lötfläche verursaachen a Risiko vu Kontaminatioun, wat zu Zouverlässegkeetsprobleemer féiere kann (schlecht Lötverbindungen / elektresch Feeler ), a schlussendlech d'Wahrscheinlechkeet vun aktuellen Feeler erhéijen.

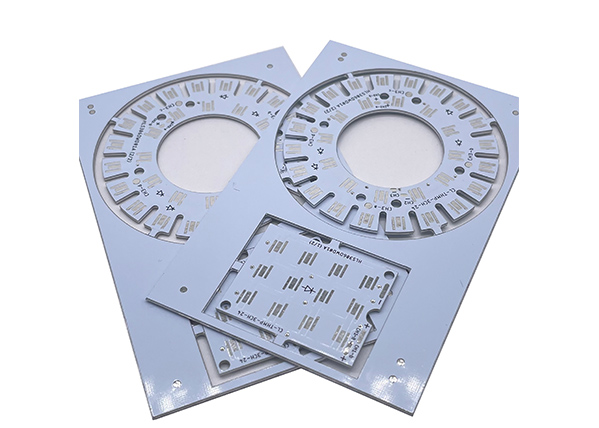

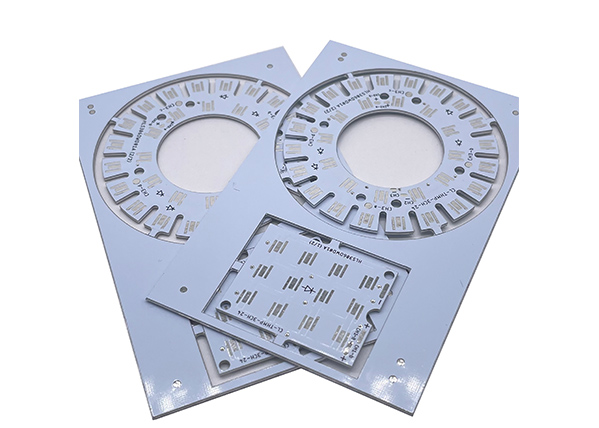

Wäiss solder Mask Aluminium Circuit Board

6. Streng kontrolléiert d'Liewensdauer vun all Uewerflächenbehandlung Virdeeler: Solderbarkeet, Zouverlässegkeet a reduzéiert Risiko vu Feuchtigkeitintrusioun. Risiken fir dëst net ze maachen: Solderbarkeetproblemer kënnen optrieden wéinst metallographesche Verännerungen an der Uewerflächefinanz vun eelere Brieder, a Feuchtigkeitintrusioun kann Delaminatioun verursaachen, banneschten Schichten a Lachmaueren während der Montage an/oder aktueller Benotzung Trennung (oppe Circuit), etc. den Uewerfläch Zinn Sprayprozess als Beispill, d'Dicke vum Zinnspray ass ≧1.5μm, an de Service Liewen ass méi laang. 7. Héich Qualitéit Plug Lach Virdeel: Héich Qualitéit Plug Lächer an der PCB Fabréck wäert de Risiko vun Echec während Assemblée reduzéieren. Risiko fir dëst net ze maachen: Chemesch Reschter aus dem Gold-Immersiounsprozess kënnen an de Lächer bleiwen, déi net voll verstoppt sinn, wat Problemer wéi Solderbarkeet verursaacht.Zousätzlech kënnen et och Zinnpärelen an de Lächer verstoppt sinn.Wärend der Assemblée oder der aktueller Benotzung kënnen d'Zinnpärelen ausdrécken an e Kuerzschluss verursaachen. 8. D'Toleranz vu CCL entsprécht den Ufuerderunge vum IPC 4101 ClassB / L Virdeel: Knapp Kontroll vun dielektrescher Schichtdicke reduzéiert Ofwäichung vun der erwaart elektrescher Leeschtung. Risiko fir dat net ze maachen: Elektresch Leeschtung kann net spezifizéiert Ufuerderunge entspriechen, a Komponenten aus der selwechter Batch kënne wäit an der Ausgang / Leeschtung variéieren. 9. Strikt kontrolléiert d'Toleranze vu Formen, Lächer an aner mechanesch Funktiounen Virdeel: Dicht kontrolléiert Toleranzen verbesseren d'Dimensiounsqualitéit vum Produkt - verbessert Fit, Form a Funktioun. Risiken fir dëst net ze maachen: Probleemer während der Assemblée, wéi Ausriichtung / Maten (Problemer mat Press-Fit Pins ginn nëmmen entdeckt wann d'Assemblée fäerdeg ass).Zousätzlech kann d'Montage an d'Basis och problematesch sinn wéinst verstäerkten Dimensiounsabweichungen.No héich Zouverlässegkeet Standarden, ass d'Lach Positioun Toleranz manner wéi oder gläich ze 0.075mm, d'Lach Duerchmiesser Toleranz ass PTH ± 0.075mm, an d'Form Toleranz ass ± 0.13mm. 10. D'Dicke vun der solder Mask ass déck genuch Virdeeler: Verbessert elektresch Isolatiounseigenschaften, reduzéiert Risiko vu Peeling oder Verloscht vun der Adhäsioun, erhéicht Resistenz géint mechanesche Schock - egal wou et geschitt! Risiko fir dat net ze maachen: Dënn Lötmaske kënnen Adhäsioun, Fluxresistenz a Hardnessproblemer verursaachen.All dës Probleemer kënnen d'Lötmaske verursaachen aus dem Bord ze trennen a schliisslech zu Korrosioun vum Kupferkreeslaf féieren.Schlecht Isolatiounseigenschaften wéinst dënnem Lötmaske, kënne Kuerzschluss verursaachen wéinst zoufälleg Leedung / Bogen.

Anerer, w.e.g. rfq, hei!

English en

English en